ii2dcam.sdc: Synopsys design constraints file Design constraints and timing assignments. reduction: C-shell script: Wide pipelined reduction function generator.

pe: C-shell script: Priority-encoder recursive generator.mux: C-shell script: Wide pipelined multiplexer generator.syn: C-shell script: A run-in-batch synthesis flow manager.sim: C-shell script: A run-in-batch simulation flow manager.

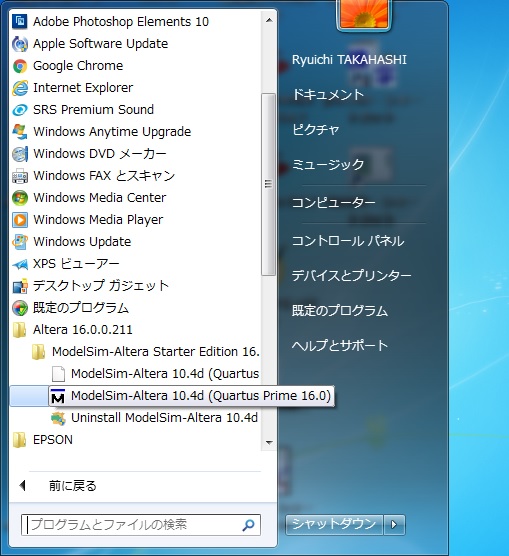

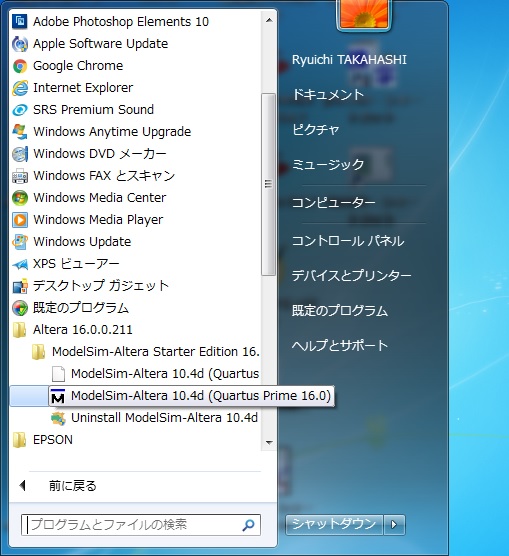

altera.14.0.ubc.csh: C-shell script: Setup environment variables and Altera 14.0 CAD flow from The University of British Columbia (UBC). altera.13.1.ubc.csh: C-shell script: Setup environment variables and Altera 13.1 CAD flow from The University of British Columbia (UBC). altera.12.0.ubc.csh: C-shell script: Setup environment variables and Altera 12.0 CAD flow from The University of British Columbia (UBC). fccm2015-slides.pdf: The 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2014) slides. fccm2015-paper.pdf: The 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2014) paper. LICENSE: BSD 3-Clause ("BSD New" or "BSD Simplified") license. ModelSim Altera Edition version 10.0d (modelsim_ase) has been used to simulate the Verilog implementation.įurthermore, the run-in-batch synthesis and simulation flow managers have been implemented using C-Shell, hence a /bin/csh should be available in the m. Quartus II version 14.0 has been used to synthesize the Verilog implementation. This project has been tested intensively using Altera's Design Suite version 14.0 Specifically: Lemieux, "Modular SRAM-based Binary Content-Addressable Memories," he 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2015), May 2015. Please refer to the full paper for more information:Ī.

altera.14.0.ubc.csh: C-shell script: Setup environment variables and Altera 14.0 CAD flow from The University of British Columbia (UBC). altera.13.1.ubc.csh: C-shell script: Setup environment variables and Altera 13.1 CAD flow from The University of British Columbia (UBC). altera.12.0.ubc.csh: C-shell script: Setup environment variables and Altera 12.0 CAD flow from The University of British Columbia (UBC). fccm2015-slides.pdf: The 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2014) slides. fccm2015-paper.pdf: The 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2014) paper. LICENSE: BSD 3-Clause ("BSD New" or "BSD Simplified") license. ModelSim Altera Edition version 10.0d (modelsim_ase) has been used to simulate the Verilog implementation.įurthermore, the run-in-batch synthesis and simulation flow managers have been implemented using C-Shell, hence a /bin/csh should be available in the m. Quartus II version 14.0 has been used to synthesize the Verilog implementation. This project has been tested intensively using Altera's Design Suite version 14.0 Specifically: Lemieux, "Modular SRAM-based Binary Content-Addressable Memories," he 23rd IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM'2015), May 2015. Please refer to the full paper for more information:Ī.

LICENSE: BSD 3-Clause ("BSD New" or "BSD Simplified") license. A run-in-batch flow manager to simulate and synthesize various designs with various parameters in batch using Altera's ModelSim and Quartus is also provided. Lemieux The University of British Columbia (UBC) 2014 Ī fully parameterized and generic Verilog implementation of the suggested modular SRAM-based indirectly-indexed 2D hierarchical-search BCAM (II2DCAM),together with other approaches are provided as open source hardware. Modular SRAM-based Indirectly-indexed 2D -# Binary Content Addressable Memory II2DCAMĪmeer M.

0 kommentar(er)

0 kommentar(er)